The performance of the processor is defined by the instruction set architecture designed in it. As both software and hardware are required for functioning of a processor, there is dilemma in deciding which should play a major role. Major firms like Intel argues that hardware should play a major role than software. While, Apple’s argument is that software should play a major role in processors architecture. The two major instruction sets architectures are

- CISC (Complex Instruction Set Computing)

- RISC (Reduced Instruction Set Computing)

CISC Architecture

In the early days machines were programmed in assembly language and the memory access is also slow. To calculate complex arithmetic operations, compilers have to create long sequence of machine code. This made the designers to build an architecture , which access memory less frequently and reduce burden to compiler. Thus this lead to very power full but complex instruction set.

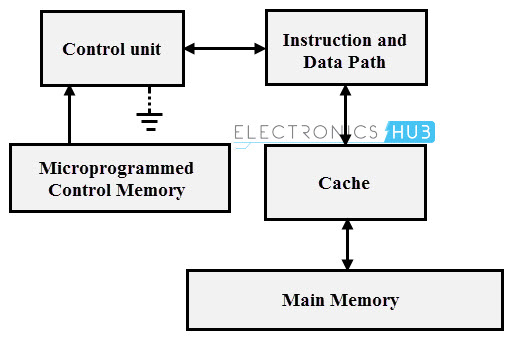

CISC architectures directly use the memory, instead of a register file. The above figure shows the architecture of CISC with micro programmed control and cache memory. This architecture uses cache memory for holding both data and instructions. Thus, they share the same path for both instructions and data. CISC has instructions with variable length format. Thus, the number of clock cycles required to execute the instructions may be varied. Instructions in CISC are executed by micro program which has sequence of microinstructions. Let us see an example: Addition of two numbers can be calculated as follows. ADD 1:1 , 2:2

The above shown instruction is divided into a number of micro instructions. Initally,it stores the data in two separate registers then decodes finally, execute This result is stored in MBR register. After this the two registers were cleared automatically. Thus to execute all these steps a complex circuitry is required.

Advantages of CISC Architecture

Microprogramming is easy to implement and much less expensive than hard wiring a control unit. It is easy to add new commands into the chip without changing the structure of the instruction set as the architecture uses general-purpose hardware to carry out commands. This architecture makes the efficient use of main memory since the complexity (or more capability) of instruction allows to use less number of instructions to achieve a given task. The compiler need not be very complicated, as the micro program instruction sets can be written to match the constructs of high level languages.

Disadvantages of CISC Architecture

A new or succeeding versions of CISC processors consists early generation processors in their subsets (succeeding version). Therefore, chip hardware and instruction set became complex with each generation of the processor. The overall performance of the machine is reduced because of slower clock speed. The complexity of hardware and on-chip software included in CISC design to perform many functions.

Examples of CISC processor

RISC (Reduced Instruction Set Computer) Architecture

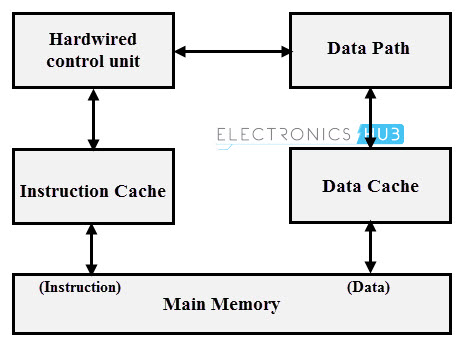

Although CISC reduces usage of memory and compiler, it requires more complex hardware to implement the complex instructions. In RISC architecture, the instruction set of processor is simplified to reduce the execution time. It uses small and highly optimized set of instructions which are generally register to register operations. The speed of the execution is increased by using smaller number of instructions .This uses pipeline technique for execution of any instruction. The figure shown below is the architecture of RISC processor, which uses separate instruction and data caches and their access paths also different. There is one instruction per machine cycle in RISC processor.

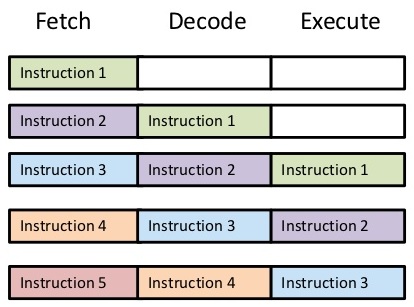

The pipelining technique allows the processor to work on different steps of instruction like fetch, decode and execute instructions at the same time. Below is image showing execution of instructions in pipelining technique. Generally, execution of second instruction is started, only after the completion of the first instruction. But in pipeline technique, each instruction is executed in number of stages simultaneously. When the first stage of first instruction is completed, next instruction is enters into the fist stage. This process continuous until all the instructions are executed.

Let us see an example : Adding of two numbers can be as shown below. LOAD A, 2:3 LOAD B, 5:2 SUM A, B STORE 2:3, A

From the above it can be seen that Addition requires four steps in RISC processor Though many instructions were required in RISC, time taken by these instructions to complete execution is same as time required to execute “ADD” in CISC. The design of the control unit is also simple due to the limited number of instructions.

Examples of RISC processors

This architecture include alpha, AVR, ARM, PIC, PA-RISC, and power architecture.

Advantages of RISC Architecture

The performance of RISC processors is often two to four times than that of CISC processors because of simplified instruction set. This architecture uses less chip space due to reduced instruction set. This makes to place extra functions like floating point arithmetic units or memory management units on the same chip. The per-chip cost is reduced by this architecture that uses smaller chips consisting of more components on a single silicon wafer. RISC processors can be designed more quickly than CISC processors due to its simple architecture. The execution of instructions in RISC processors is high due to the use of many registers for holding and passing the instructions as compared to CISC processors.

Disadvantages of RISC Architecture

The performance of a RISC processor depends on the code that is being executed. The processor spends much time waiting for first instruction result before it proceeds with next subsequent instruction, when a compiler makes a poor job of scheduling instruction execution. RISC processors require very fast memory systems to feed various instructions. Typically, a large memory cache is provided on the chip in most RISC based systems.

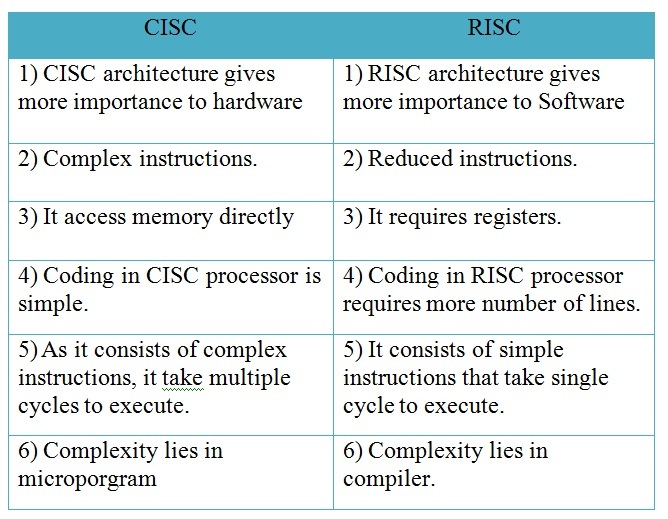

RISC Vs CISC

Comment * Name * Email * Website

Δ

![]()